161 руб.

Заказать

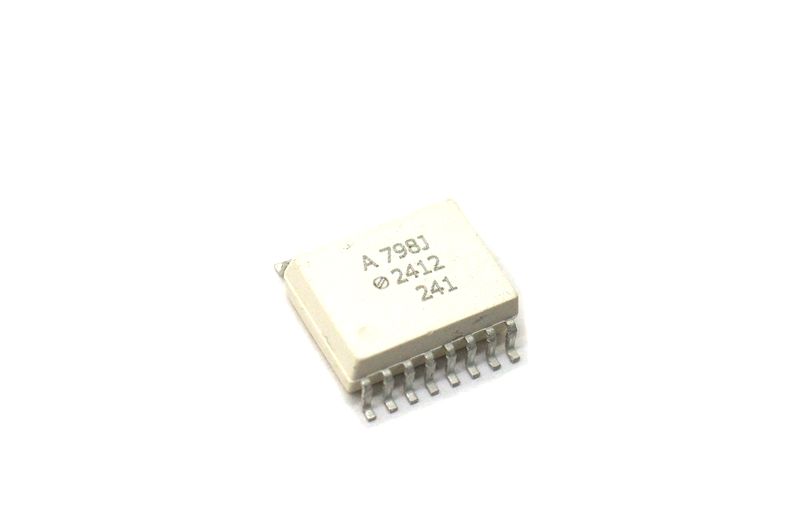

ACPL-798J

Up to 25 MHz external clock input range

LVDS clock and data interface.

1-bit, second-order sigma-delta modulator

16 bits resolution no missing codes (12 bits ENOB)

75 dB Typical SNDR

3.5 V/°C maximum offset drift

±1% maximum gain error

±200 mV linear range with single 5 V supply

–40°C to +105°C operating temperature range

SO-16 package

25 kV/μs common-mode transient immunity